Test Driven Development für Hardware – 400 Transistoren, 1200 Widerstände und keine Bugs?

Vortrag

In der Softwareentwicklung sind umfangreiche Tests, die automatisch mit jeder Codeänderung ausgeführt werden inzwischen Standard. Auch bei der Entwicklung von großen CPUs in VHDL, Verilog oder anderen Hardwarebeschreibungssprachen gehören Tests zu der Norm. Aber gerade bei kleineren oder analogen Projekten bleibt einem Bastler häufig nur die Möglichkeit, sich auf seine eigene Sorgfältigkeit zu verlassen.

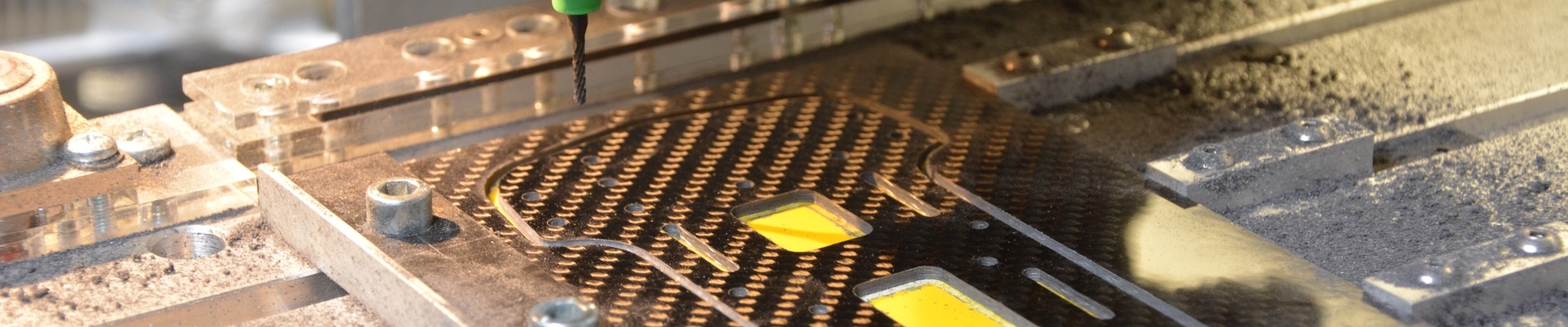

Dieser Vortrag gibt einen Überblick über ein laufendes Projekt, in dem eine CPU mit Unterstützung von automatisierten Tests entwickelt wird. Hierzu werden die EAGLE-Schaltpläne von Python-Skripten automatisch in ein SPICE-kompatibles Format umgewandelt, simuliert und mit Tests abgeglichen.

Vorkenntnisse

Ein Grundverständnis von elektrischen Schaltplänen und Board Design ist hilfreich.

Lernziele

Das Ziel dieses Vortrags ist, die Besucher anzuregen, über modernere Methoden der Schaltungsentwicklung nachzudenken. Die in dem Vortrag skizzierte Vorgehensweise ist auf diese Art sicherlich nicht auf viele Projekte übertragbar, aber gerade im Hobbybereich hat sich in der Methodik der Schaltungsentwicklung in den letzen 20 Jahren nicht viel verändert.

Dieser Vortrag zeigt, wie man mit Hilfe und verschiedenen Tools (Python, SPICE) seine Entwicklung vereinfachen und die Wahrscheinlichkeiten von teuren Ausbesserungen / Neubestellungen reduziert kann.

Referent

//

Philip Peter

Philip Peter

beschäftigt sich in seinem Hauptberuf als Softwareentwickler häufig eher mit großen Java-, Swift- oder C++-Projekten. Dagegen gehen seine Hobbybasteleien in die andere Richtung: Hier bschäftigt er sich mit kleinen Sensoren mit einem ESP8266-WLAN-Modul oder einem kleinen 8-Bit-Mikrokontroller. Eines seiner aktuellen Projekte ist die Entwicklung einer CPU aus diskreten Transistoren und Widerständen.